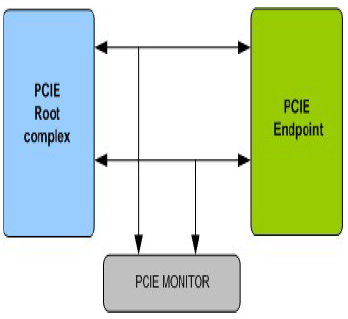

Description

PCIe Verification IP provides an smart way to verify the PCIe bi-directional bus. The PCIe Verification IP is fully compliant with version 1.0/2.0/2.1/3.0/4.0/ 5.0/6.0 of the PCIe Specification and provides the following features. PCI Express Verification IP is supported natively in System Verilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env PCI Express Verification IP comes with optional Smart Visual Protocol Debugger which is GUI based debugger to speed up debugging.

Features

-

Full MIPI DSI-2 Tx and Rx functionality.

-

Supports PCI Express specs 1.0/2.0/2.1/3.0/4.0/5.0/6.0

-

Supports mPCIe

-

Supports PIPE, PCS/PMA, Message Bus and SERDES interface

-

Supports MPHY RMMI and serial interface • All error injections in MPHY layer • All protocol checks for MPHY layer • All PWM and HS gears as supported by MPCIe • All lane configurations as supported by MPCIe • Automatic clock recovery • Supports asymmetrical lane configuration • Supports dynamic bandwidth scalability

-

Supports UVM and Verilog APIs supplied as well as C DPI exports

-

Support for Generations 1.0/2.0/2.1/3.0/4.0/5.0/6.0 including SSC

-

Configurable Link widths as x1,x2,x4,x8,x12,x16,x32

-

Supports Up configuration, polarity inversion, and lane-to-lane skew

-

Supports ASPM and Software controlled Power Management

-

Supports Full LTSSM state machine

-

Supports Full DL state machines

-

Checkers verify protocol timing checks and functional accuracy at each layer

-

Supports Queuing for 8 VCs with configurable depth

-

Configurable TC to VC queue mapping

-

Support for multiple Requestor / Completer applications, including user supplied applications

-

User interface for direct TLP queuing and receipt

-

Checks all TLPs for correct formation of header, payload, prefix and ECRC

-

Supports SERDES model with clock recovery

-

Configurable Spread Spectrum Clocking (SSC)

-

Supports Gen 1, Gen 2, 8b/10b, Gen 3, Gen 4 and Gen 5 128b/130b encoding

-

Supports Gen 6 1b/1b encoding

-

Configurable timers and timeouts

-

Supports Functional coverage for complete PCI Express features

-

Supports Lane Margining at Receiver

-

Supports VF 10-Bit Tag Requester

-

Supports Link management DLLP

-

Supports IDE Functionality

-

Supports DOE, SR-IOV

Deliverables

-

Complete regression suite containing all the PCIe testcases to certify PCI Express Root complex and End point.

-

Examples showing how to connect various components, and usage of BFM and Monitor.

-

Detailed documentation of all class, task and function's used in verification env. Documentation also contains User's Guide and Release notes

![]()