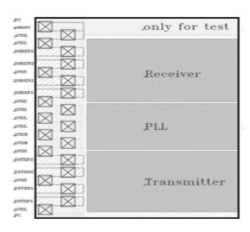

A high performance, high-speed SERDES IP called USB3.1Type-C PHY is created for semiconductors that provide high bandwidth data connection while using less power. A specific design for USB 3.1 type-C applications is the USB 3.1Type-C PHY IP. A dedicated PCS can be provided together with the USB 3.1 Type C PHY IP to complete functionality of various applications, including elastic buffer, scramble/de-scramble, data encoding/decoding, PRBS generation/checking, registers control and testing. Depending on the customer's choice, PCS is offered as either a hard or soft macro; additionally, the PCS specification will be made available separately. Using a test bench constructed in Verilog HDL, the NC-Verilog simulation software verifies PHY functionality.

Deliverables

Graphic Data System II File Including Layer Mapping .

LEF Files Depicting Placement and Routing Topology

Timing and Power Characterization Data in Liberty Format

Verilog Model Depicting Functional Behavior

Standard Delay Format Timing Specifications for Circuit Netlist

Application Notes Offering Layout Best Practices

LVS and DRC Verification Results Summary