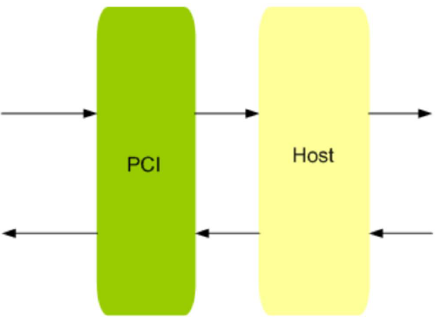

Description

PCI MASTER/SLAVE interface provides full support for the PCI MASTER SLAVE synchronous serial interface, compatible with PCI 2.0 specification. Through its PCI MASTER SLAVE compatibility, it provides a simple interface to a wide range of low-cost devices. PCI MASTER SLAVE IP is proven in FPGA environment. The host interface of the PCI MASTER SLAVE can be simple interface or can be AMBA APB, AMBA AHB, AMBA AXI, VCI, OCP, Avalon, PLB, Tilelink, Wishbone or Custom protocol.

Features

-

Compliant with PCI version 2.0 Specification

-

Supports 32-bit address and data

-

Supports all types of devices select delays

-

Supports arbiter which is 100% PCI specification compliant

-

Supports all types of error detection

-

Provides parity on both data and address and allows implementation of robust client platforms.

-

Full multi-master capability allowing any PCI master peer-to-peer access to any PCI master/target.

-

Synchronous bus with operation up to 66 MHz

-

Forward and backward compatibility with PCI 66 MHz

-

Customization and integration service is available

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to microprocessor/microcontroller devices

Benefits

-

Single site license option is provided to companies designing in a single site.

-

Multi sites license option is provided to companies designing in multiple sites.

-

Single Design license allows implementation of the IP Core in a single FPGA bitstream and ASIC.

-

Unlimited Designs, license allows implementation of the IP Core in unlimited number of FPGA bitstreams and ASIC designs.

Deliverables

-

The PCI Master/Slave interface is available in Source and netlist products.

-

The Source product is delivered in plain text Verilog. If needed VHDL, SystemC code can also be provided.

-

Easy to use Verilog Test Environment with Verilog Testcases

-

Lint, CDC, Synthesis, Simulation Scripts with waiver files

-

IP-XACT RDL generated address map

-

Firmware code and Linux driver package

-

Documentation contains User's Guide and Release notes.

![]()