Description

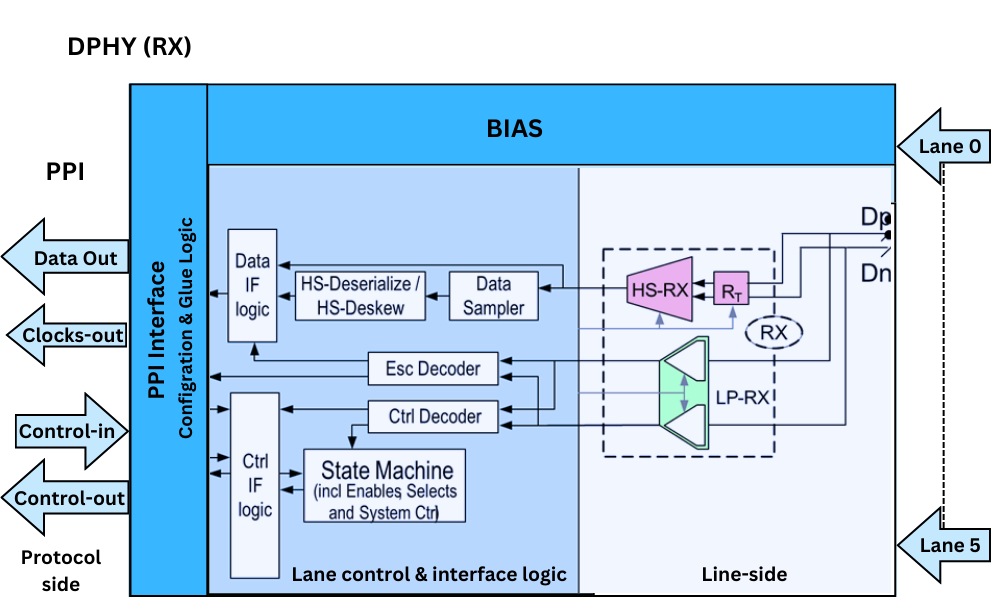

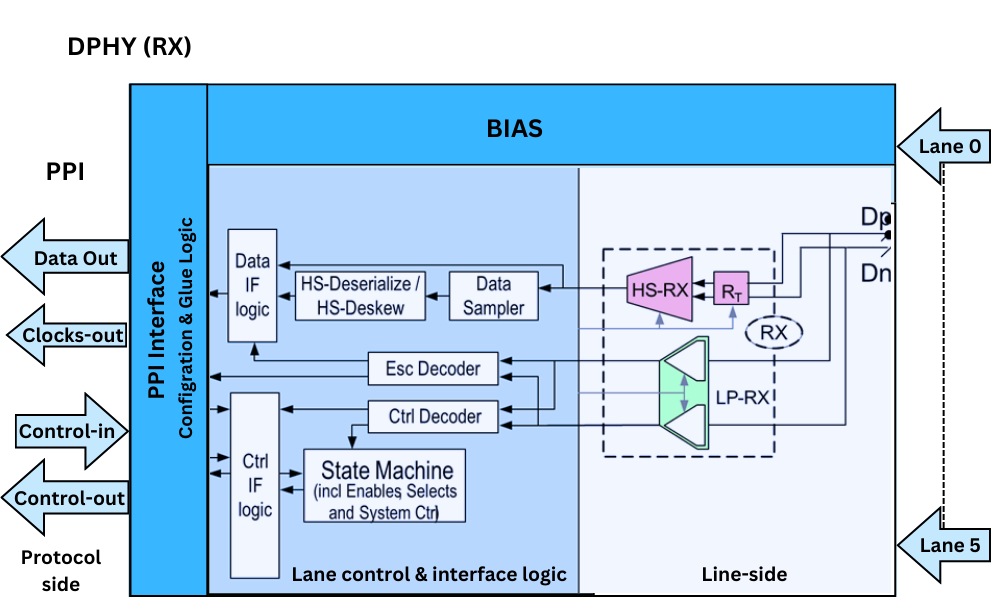

The MIPI D-PHY Rx IP Core in 28HPC+ aligns precisely with the D-PHY specification version 1.2, facilitating support for the Display Serial Interface (DSI) and MIPI Camera Serial Interface (CSI-2) protocols. This Rx PHY architecture includes one clock lane and four data lanes. Functionally, it integrates a digital backend for precise I/O operation management and an analog frontend for efficient generation and reception of electrical level signals. Moreover, it incorporates an internally calibrated termination resistor, ensuring optimized performance. These combined features establish it as a reliable solution for seamless data transmission and reception, meeting industry standards with excellence.

Features

-

Compliant to MIPI Alliance Standard for D-PHY specification Version 1.2

-

Supports standard PPI interface compliant to MIPI Specification

-

Supports synchronous transfer at high speed mode with a bit rate of 80-2500 Mb/s

-

Supports asynchronous transfer at low power mode with a bit rate of 10 Mb/s

-

Supports ultra-low power mode, high speed mode and escape mode

-

Supports one clock lane and up to four data lanes

-

Data lanes support transfer of data in high speed mode

-

Supports error detection mechanism for sequence errors and contentions

-

Supports contention detection

-

Configurable skew option for each Clock and Data lanes

-

Testability for TX, RX and PLL

-

Silicon Proven in TSMC 28HPC+

Deliverables

-

GDSII & layer map

-

Place-Route views (.LEF)

-

Liberty library (.lib)

-

Verilog behaviour model

-

Netlist & SDF timing

-

Layout guidelines, application notes

-

LVS/DRC verification reports