Description

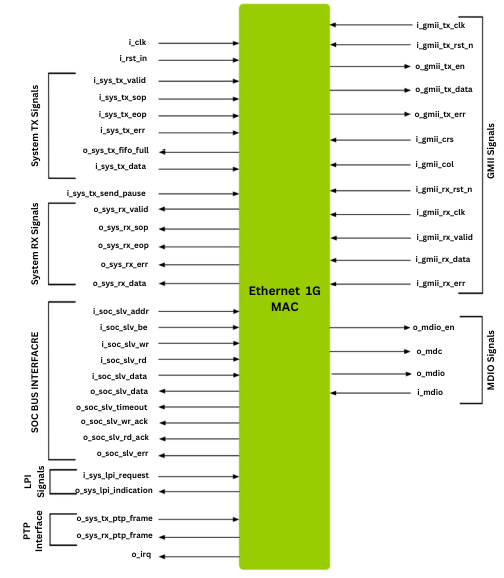

Ethernet 1G MAC IP Core is compliant with the IEEE 802.3.2018 specification's Ethernet protocol standard and may be seamlessly integrated into any SoC or FPGA program. It can handle a wide range of host bus interfaces, including AHB, AHB-Lite, APB, AXI, AXI-Lite, Tilelink, OCP, VCI, Avalon, PLB, Wishbone, and custom buses, making it simple to integrate into any design architecture and additionally, any technology can be used to implement the Ethernet 1G MAC IP. Verilog RTL implementations of the Ethernet 1G MAC IP can be found in FPGAs and ASICs. With FPGA, the Ethernet 1G MAC IP is verified. RTL code, test scripts, and a test environment for comprehensive simulation are all included in the core.

Features

-

Compliant with IEEE Standard 802.3.2018 specification

-

Support for Full duplex and Half duplex mode

-

Supports GMII and MII Interfaces

-

Supports MDIO (Clause 22 and Clause 45) Interface

-

Supports Programmable Inter Packed Gap(IPG) and Preamble length

-

Provides detailed statistics as per the specification

-

Supports IEEE Standard 802.3az Energy Efficient Ethernet (EEE)

-

Supports IEEE Standard 802.1Q and IEEE Standard 802.1ad VLAN

-

Supports Wake-on-LAN

-

Supports Loopback Functionality

-

Supports Control frame and Jumbo frame

-

Supports transmit and receive FIFO interface

-

Supports FCS (CRC) transmission and reception

-

Supports Pause frame based flow control in full duplex mode

-

Supports AXI stream Interface for System Interface

-

In house UNH compliance tested

-

Optional support for TCP/IP

-

Optional support for IEEE Standard 1588-2008 PTP

-

Optional support for DMA support for both transmit and receive side

-

Optional support for RMII, RGMII and TBI interfaces

-

Fully synthesizable

-

Static synchronous design

-

Positive edge clocking and no internal tri-states

-

Scan test ready

-

Simple interface allows easy connection to Microprocessor/Microcontroller devices

Deliverables

-

Verilog RTL design

-

Scripts for Linting, CDC analysis, and Synthesis along with waiver files

-

Reports for Linting, CDC analysis, and Synthesis

-

IP-XACT RDL-generated address map

-

Package containing firmware code and Linux drivers

-

Comprehensive technical documentation

-

Verilog Test Environment with user-friendly test cases

Benefits

-

Fully compliant, silicon-proven core

-

Comes with Verilog testbench and option to buy full advanced System Testbench

-

Support directly from engineer who designed the code

-

Based on RMM (Re Use Methodology Manual guidelines)

-

Supports all the Synthesis tools

![]()